About the Rule Compiler

I've managed to get the pyRete Rule Compiler to generate a directed (acyclic) graph which, at least, resembles a Rete Network. There are still some situations it can't handle, but it works quite well in most situations.

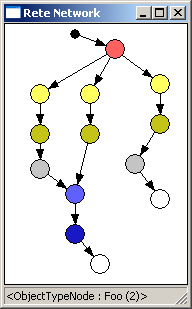

>>> import pyReteThe last line pops up the wxWidgets Rete Network Viewer which looks like this:

>>> class Foo(pyRete.Fact):

... def __init__(self, n):

... self.n = n

>>> @pyRete.Rule

... def rule1(foo = Foo):

... if foo.n == 1:

... pass

>>> @pyRete.Rule

... def rule2(foo1 = Foo, foo2 = Foo):

... if foo1.n > 0 and foo2.n > 1 and foo1.n > foo2.n:

... pass

>>> ruleengine = pyRete.RuleEngine(None)

>>> ruleengine.addRules([rule1, rule2])

+O+A+P

=O=O+A+A+B+P

>>> ruleengine.showReteNetwork()

Rule2 is the left branch, rule1 is the right branch in this graph. The red node is an ObjectTypeNode, the yellow ones are Alpha Nodes, the green/yellow ones are Alpha Memories, the grey ones are LeftInputAdapters, the blue one is a Beta Node, the darker blue is a Beta Memory and the white ones are Production Nodes.

There are a few things that doesn't look good. For example, the Beta Memory shouldn't be there in rule2 and the LeftInputAdapter shouldn't be there in rule1 but I'm getting closer and closer...

2 kommentarer:

You've quite a bit of progress in a short amount of time. congrats!

Thanks Peter.

I hope to be able to have enough of the implementation to run some performance tests (Manners et al) soon. And then, the real work can begin ;-)

Skicka en kommentar